数据传输和实时处理子系统(以下简称传输系统)是海上地震探测系统的重要组成部分。其传输速率与稳定性直接影响海上地震信息的采集质量,高性能的传输系统可以保证数据传输的高速度和高准确度。

数据传输和实时处理子系统(以下简称传输系统)是海上地震探测系统的重要组成部分。其传输速率与稳定性直接影响海上地震信息的采集质量,高性能的传输系统可以保证数据传输的高速度和高准确度。海上地震探测传输系统在国外已有成熟的产品,但其成本较高,并且多采用设置时间戳的方法传输不同传输板的数据[1],要求电缆外部采用大量缓存,以识别时间戳以使数据有序上传。为满足海上地震信息采集的需要,传输系统应具有传输速率高(大于100 Mb/s)、传输距离长(传输板间距可达100 m)的特点。国内传输系统大多采用光纤作为传输介质[2],其优点是传输速率高,无中继传输距离远,无电磁干扰,但是其光电转换接口部分成本较高且不易维护,安装不便。针对以上问题,设计了一种海上地震探测传输系统。此系统采用流水线逐级上传数据的方法解决了电缆外部需要大量缓存的问题[1],大大减少了成本和空间。采用基于LVDS和双绞线技术的传输方式,实现了100 m长度下160 Mb/s数据的稳定传输。此系统在满足高速率传输的同时,具有成本低,使用方便,安装容易,体积小等优点,使电缆传输成功应用于地震采集数据传输系统。

1 系统结构

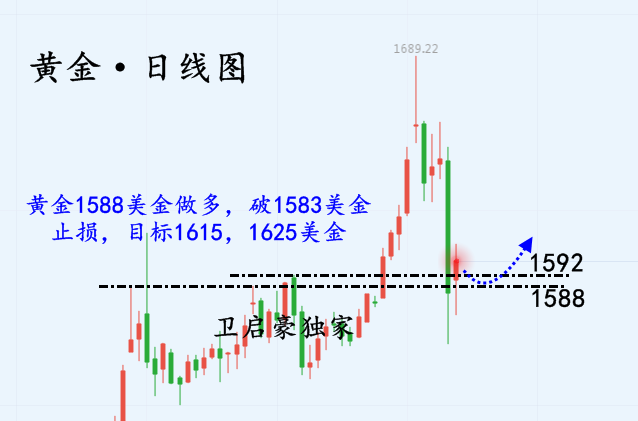

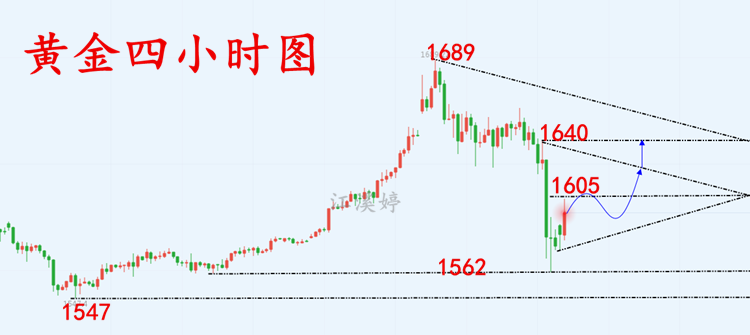

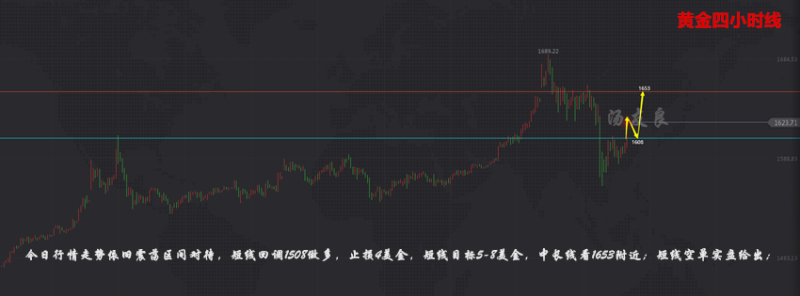

海上地震探测传输系统的结构框图如图1所示。该系统由多个数据采集和传输单元组成,每个数据采集和传输单元被放置在海上的水下工作区。传感器采用压电传感器或光纤传感器,用于采集水下的地震信号;采集板主要由前置放大、模数转换电路和FPGA(Field Programmable Gate Array)组成,用于将地震信号放大滤波后转换成数字信号传送到传输板;传输板主要由LVDS收发电路、预加重均衡电路和FPGA组成,用于接收本地采集板上传的数据、打包成帧,并完成数据在级联传输板间的有序上传;上位机通过PCI采集板采集传输板上传的数据并存储,同时发送对各传输板和采集板的控制命令,控制地震信号的有序采集。

2 系统传输板硬件电路设计

2.1 传输板设计参数要求

该系统采集板的部分设计参数要求如下:传输板板间间距100 m,每条拖缆需要级联30个传输板,水下连接采集板的拖缆长3 km;每个传输板下设一个采集板,每个采集板下设16个传感器,传感器每次采样24 bit,采样率4 kHz。

2.2 传输板的硬件设计

传输板硬件框图如图2所示。由于系统中各传输板的间距为100 m,而且数据传输率要求保证为160 Mb/s,故采用LVDS串化芯片MAX9205与预加重芯片CLC006组成数据发送端,采用LVDS解串芯片MAX9206与均衡芯片CLC014组成数据接收端。数据接收端与发送端共同完成高速长距离数据传输。由于下传命令速率较低,采用RS485传输,芯片选用MAX3490。双绞线具有尺寸小、柔软性好、抗干扰能力强、价格便宜等特点,系统采用内含4对的六类双绞线传输数据信号、命令信号及同步信号。FPGA作为传输板的核心,主要完成三方面的工作:(1)命令解析及下传,通过RS485方式接收上位机命令,对其进行解析后下传送采集板,同时发送至后续传输板;(2)数据接收及处理,接收本地采集板数据并打包成帧;(3)完成数据流水线。

2.3 LVDS电路实现

LVDS是一种小振幅差分信号技术,使用幅度非常低的信号(约350 mV)通过一对差分线或平衡电缆传输数据[3]。LVDS功耗小,速率快,可直接相连[4],但直连的传输距离短,通常只有几米,故本系统采用了预加重和均衡电路来扩展传输距离。

如图3所示,信号先通过MAX9205并串转换后输出,然后经隔直和电压匹配后传送给由CLC006组成的信号驱动电路,信号峰峰值被提升后经阻抗匹配并输出,其中通过改变R5的大小可调整CLC006输出信号的峰峰值。信号被提升前与提升后的波形如图3所示。

信号经100 m双绞线传输后峰峰值降低且上升沿变缓,如图4中C点波形所示。

接收端经电阻网络进行阻抗匹配,电阻阻值采用如下公式进行计算:

其中Z0为双绞线特征阻抗,VPP为信号峰峰值。接收到的信号经由CLC014芯片组成的均衡电路进行信号均衡后输入到MAX9206中,图4中给出了C、D两点的测量波形图。

3 FPGA中数据的传输过程

3.1 传输板的命令解析及下传过程

命令通道采用自定义串口协议,将命令帧格式设计为两个9位的字节,其中一个字节传送命令,另一个字节传送参数。每个字节中的第9位用于作为命令和数据的标识位。

命令下传时有两种模式,一种为总线模式,一种为级联模式,使用总线模式比级联模式的优势在于不用使信号经FPGA解析,信号延迟小,缺点为传输距离有限,所以采用命令经过传输板后重新驱动的方式发送命令,同时接收进本地FPGA解析。

总线模式中命令都采用广播方式接收,动态设置传输板包号成为一个关键问题,设置包号即为把传输板以距离船体远近的方式设置序号。由于所有传输板同等接收命令,所以不能像级联模式那样通过命令经各传输板解析下传的方式区别各传输板以达到动态设置包号的目的。为解决此问题,系统采用的方法为:先下传点名命令,各传输板接收到此命令后通过级联的数据通道发送一点名帧,点名帧中包含包号信息,初始包号信息为“0”,当传输板接收到点名帧后,把点名帧中的包号信息加一后继续下传,依次类推,每个传输板最后发送的点名帧中的包号就是自身的包号。

3.2 传输板的数据处理及上传过程

为了保证传输速率,采集板的数据分两路传送到传输板,传输板采用“乒乓结构”的方式把两路数据合成一路,并添加状态信息与CRC(Cyclical Redundancy Check)16校验位,最后通过8B/10B的编码后将数据存入本地FIFO中。由于MAX9205与MAX9206数据线都是10 bit,用8B/10B编码在完成直流均衡功能的同时方便了程序的编写。

当各传输板接收到上位机发送的“采集数据”指令后,一方面各传输板将命令下传到与之对应的采集板,使采集板采集并上传一组数据;另一方面传输板将上传一帧本地FIFO中的数据到下一级传输板中,同时把接收到的上一传输板数据存入一个异步FIFO中,待上传本地数据完毕后再依次上传接收并存入异步FIFO中的数据,依此类推,直至把最后一个传输板上的数据也上传至其下一个传输板。

图5为使用Quartus II 9.0中的Signal Tap II工具查看到的从尾包数第三块传输板内部信号的实际测量信号图。其中a3为解析后同步采集命令使能,dataout为数据发送端,next为接收后续板数据端。图5中最下面四个信号为发送状态机信号,其中SELF为发送本地FIFO数据,SYN为发送数据间隙时的同步序列,NEXT为发送后续数据,配合bendififo与rxfifo的读写信号完成数据的有序上传,其中一帧数据为76 B。

3.3 LVDS传输失锁问题的软件设计

MAX9206在接收数据时会从数据中提取时钟,如果提取不到时钟,则称为失锁。失锁后MAX9206不再输出有效数据,直到再次锁定时钟数,数据输出再次有效。由于传输线路存在各种噪声,长时间运行时要求系统尽量不出现失锁情况,在出现失锁时要求能尽快再次锁定时钟。

首先LVDS接口电路在系统上电后由FPGA将MAX9205的SYN脚(用于使接收端MAX9206更快地锁定接收端MAX9205的时钟)置为高电平2 ms,用于使MAX9205和MAX9206锁定自身的时钟,然后接收端MAX9206锁定接收数据时钟。MAX9205的SYN引脚置为高电平时忽略输入数据,串行输出一组同步数据,数据格式为“000000111111”,目的是使MAX9206更快地从接收数据中锁定时钟,2 ms后若不从MAX9205输出数据则会导致MAX9206失去接收时钟。所以在SYN引脚置为低电平时,MAX9205输出”0000011111”(同步序列),然后再加上MAX9205并转串时的起始位和终止位而组成“000000111111”,而使同步不易失锁。

为提高系统的稳定性,使失锁后能迅速再次锁定时钟,系统采用在发送数据的空闲时间里发送同步序列的方法,在发送同步序列时至多42个周期时钟便会锁定。所以在发送一帧数据后发送42个周期的同步序列。这种方法虽然引入冗余,使有效数据率下降,但在数据传输率高达160 Mb/s的情况下,这种方法也完全可以满足系统要求,且空闲时发送同步序列的方法使系统更不易发生失锁,提高了系统的稳定性。

4 实验结果

实验结果如表1所示。其中情况1中为实验室正常条件下,未加干扰;情况2中在传输双绞线旁放置输2 MHz干扰源,情况3中在传输双绞线旁放置输5 MHz干扰源。

由于在海水中高频信号衰减较大,不易出现高频干扰,由实验结果可知系统较适于海上传输。

该系统采用了流水线逐级上传的方法解决了电缆外部需要大量缓存的问题。首次把基于LVDS和预加重及均衡的传输方式引入海上拖缆传输系统,实现了长距离高速率传输。经初步联调,现该系统工作正常,达到了项目对系统高速度和稳定性的要求。

参考文献

[1] 曾翔,宋克柱,唐世悦.基于光纤的多级数据采集传输系统设计[J].光纤与电缆及其应用技术,2005(6):29-31.

[2] 曾翔.地震拖缆多级数据传输系统[D].安徽:中国科学技术大学,2006.

[3] 彭勇,黄秋元.LVDS的接口电路设计[J].武汉理工大学学报.信息与管理工程版,2005(10):189-192.

[4] Stephen Kempaimen.Low Voltage Differential Signaling [J]. Insight,2005(2):15-20.

(来源:电子技术应)【免责声明】本文仅代表作者本人观点,与和讯网无关。和讯网站对文中陈述、观点判断保持中立,不对所包含内容的准确性、可靠性或完整性提供任何明示或暗示的保证。请读者仅作参考,并请自行承担全部责任。

E-mail: it@staff.hexun.com

地址:北京市朝阳区朝阳门外大街22号泛利大厦11层

邮编:100020

传真:010-85650806

客服热线:

客服热线: